Digital Calibration Technique for A/D Converters

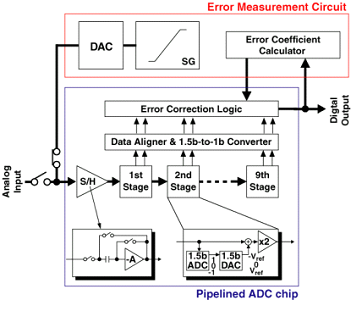

A digital calibration technique, which does not need to incorporate the error measurement circuits in the ADC core, is developed.

In the proposed method, capacitor mismatch error of the pipelined stages are estimated using an integral non-linearity plot for a ramp signal.

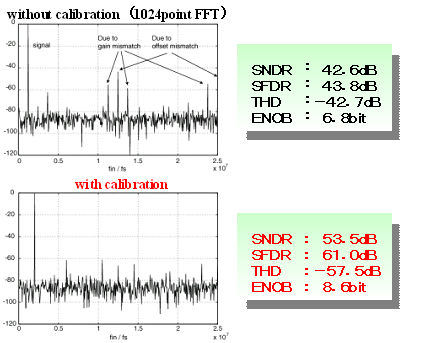

The proposed calibration method is applied to an implemented 10bit, 120Msample/s 4-channel parallel pipelined ADC chip.

As a result, this method can improve the ENOB from 6.8bit to 8.6bit in the 10bit ADC.

|

|

| Block diagram of proposed digital calibration.

| Measurement result.

|

References

- M. Furuta, S. Kawahito, D. Miyazaki, "A Digital Calibration Technique of Capacitor Mismatch for Pipelined Analog-to-Digital Converters", IEICE Trans. Electron., Vol.E85-C, No.8, pp.1562-1568, 2002

- D. Miyazaki, M. Furuta, S. Kawahito, "A 75mW 10bit 120Msample/s Parallel Piepline ADC", Proc. European Solid-State Circuits Conf., pp.719-722, 2003

- M. Furuta, S. Kawahito, D. Miyazaki, "A Digital Calibration Technique for Redundant Raidx-4 Pipelined Analog-to-Digital Converters", IEEE Trans. on Instrum. Meas., to be published

[Home] / [Research project]

Copyright(C)1999-2007, Imaging Devices Laboratory

e-mail: [email protected]